最近市场炒得火热的芯片晶圆板封装(CoWoP)技术,与现有的CoWoS封装有什么区别?对供应链有何影响?商业化前景如何?

8月5日,据追风交易台消息,摩根大通在最新研报中称,英伟达正在探索一项革命性的芯片封装技术CoWoP(Chip-on-Wafer-on-PCB),该技术有望替代现有的CoWoS封装方案。

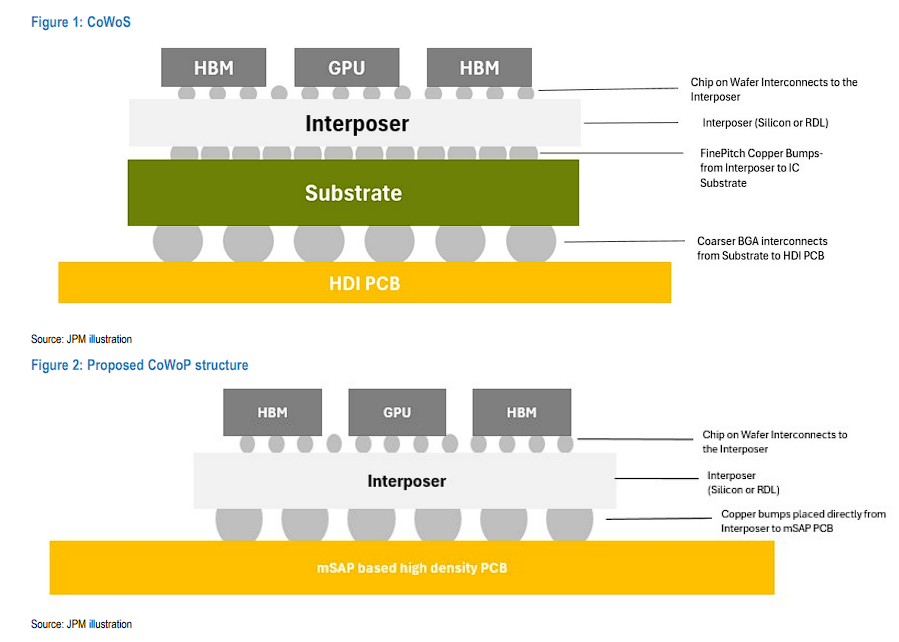

摩根大通指出,这一技术变革将利用先进的高密度PCB(印刷电路板)技术,去除CoWoS封装中的ABF基板层,直接将中介层与PCB连接。

该行还在研报中详细分析了"CoWoP"技术对于供应链的影响,认为对ABF基板厂商显然是负面消息,却是PCB制造商的重大机遇。

虽然,摩根大通分析师认为该技术在中期内商业化概率较低,主要受制于多重技术挑战,但是该行在研报中强调:

无论CoWoP是否成功量产,英伟达都通过系统级方法继续引领数据中心AI基础设施创新。

CoWoP技术原理与优劣势分析

研报称,CoWoP代表Chip-on-Wafer-on-PCB技术路径。在完成芯片-晶圆中介层制造步骤后,中介层(顶部带芯片)直接安装到PCB(也称为平台PCB)上,而不是像CoWoS工艺那样绑定到ABF基板上。

该技术的潜在优势包括:

简化系统结构,通过减少传输损耗提高数据传输效率,确保NVLink互连更高的范围; 更好的热管理性能和更低的功耗; 降低每代产品都在上升的基板成本; 潜在减少一些后端测试步骤。

然而,摩根大通认为,这项技术存在关键挑战。目前只有苹果公司采用mSAP或SLP PCB技术,但其节距尺寸更大,PCB板面积更小,因此将此技术扩展到具有更高载流能力的大型GPU仍然是技术和运营挑战。

供应链影响:IC基板负面冲击显著、PCB制造商的重大机遇

摩根大通在研报中称,对ABF基板厂商而言,这显然是负面消息,因为基板附加值可能会大幅减少或完全消失,更复杂、精细节距的信号路由将转移到RDL层(中介层),而高端PCB层承担封装内路由步骤。

摩根大通认为,对于PCB制造商,是一个重大机遇高速。研报指出:

“性能与主板高电流/电压要求之间的权衡是阻止平台PCB实现真正基板规格的主要挑战。mSAP是在实现25/25微米更精细线/间距尺寸方面最佳的PCB技术,但仍远低于ABF的亚10微米线/间距能力。”

因此,该行认为,具备先进mSAP能力以及基板/封装工艺深度知识的公司将更有优势。

中期内商业化概率较低,无碍英伟达创新领导力持续强化

摩根大通分析师认为,由于多重技术挑战,CoWoP中期内商业化的概率仍然较低。

历史上,更高的I/O数量和更精细的线/间距尺寸(CoWoS-L降至5微米,CoWoS-S约10微米)需要迁移到ABF基板。对于AI加速器,即使ABF基板也预计会在5/5线/间距尺寸之后失效。

PCB技术即使使用mSAP,目前也只能达到20-30微米的线/间距宽度,与期望性能相比仍存在较大差距。

据,大摩也表示,当前高密度互连(HDI) PCB的L/S为40/50微米,即使是用于iPhone主板的类基板PCB(SLP)也仅达到20/35微米,要将PCB的L/S从20/35微米缩小到10/10微米以下存在显著技术难度。

此外,摩根大通认为,英伟达目前确定的路线图(向CoWoS-L、CoPoS发展,在Cordelia Board中采用GPU插座)与CoWoP追求的新方向也相当矛盾。

供应链研究显示,高附加值封装生态系统参与者(如台积电)参与度不高,主要集中在PCB厂商和特定的OSAT厂商,这降低了商业化的可能性。

不过,摩根大通指出,无论CoWoP是否成功量产,英伟达都通过系统级方法继续引领数据中心AI基础设施创新。

“在半导体领域,英伟达率先推出CoWoS-L封装,探索CoWoP和CoPoS封装技术,并可能领导大规模CPO(共封装光学)应用和1.6T光学技术发展。”

摩根大通称,这种持续创新能力预计将使英伟达在未来数年内保持GPU领域的领先优势,并在与ASIC竞争中占据主导地位。